Nvidia ha annunciato il suo programma di accelerazione H100 per data center e HPC. Questa GPU PCIe 5.0 è prodotta su un nodo TSMC 4N e dispone di memoria HBM3 con larghezza di banda fino a 3 TB/s. L’Nvidia H100 succede all’attuale GPU A100.

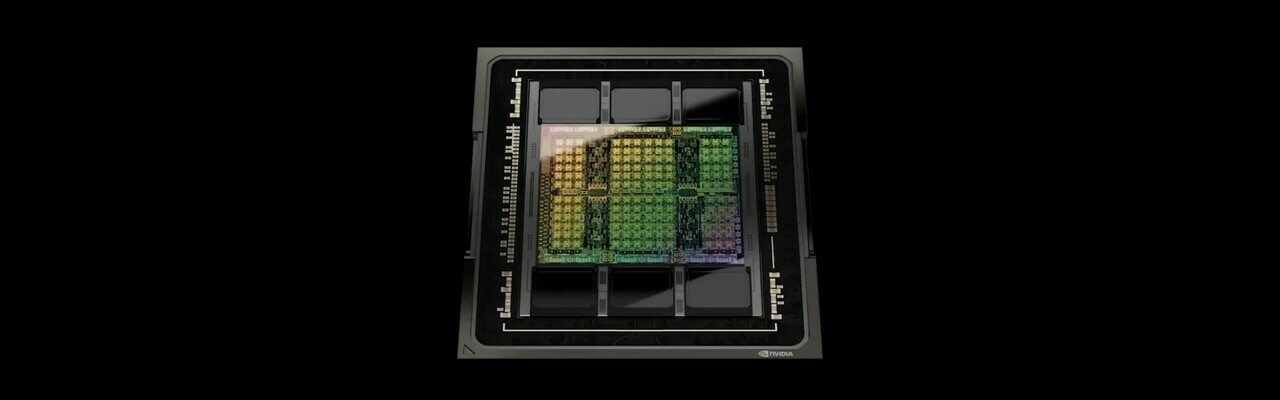

GPU Nvidia H100 Si basa su Hopper, un’architettura GPU rivolta a data center, HPC e Ampere Seguire in questo campo. H100 è composto da 80 miliardi di transistor ed è prodotto con il processo TSMC 4N. Questa è una versione modificata del processo TSMC N4, in particolare per Nvidia. Il Nvidia H100 Ancora una volta un chip monolitico, proprio come l’A100. Inizialmente, si diceva che Nvidia avrebbe offerto una GPU per data center con un design multi-chip, composta da Muore† AMD ha fatto proprio questo l’anno scorso con la serie Instinct MI200.

L’attuale A100 è prodotto su una versione modificata del processo TSMC a 7 nm ed è composto da 54,2 miliardi di transistor. Nvidia afferma che l’H100 fornisce fino a tre volte più potenza di calcolo rispetto all’A100 in fp16, tf32 e fp64 e sei volte di più in fp8. La GPU H100 ha una dimensione di 814 mm². Questo è leggermente più piccolo dell’attuale GA100, che ha colui il quale– Un’area di 826 mm².

Nvidia H100 SXM5 (a sinistra) e H100 PCIe

HBM3 per SXM5, HBM2e per variante PCIe

Nvidia offre due varianti dell’H100. L’attenzione sembra essere sulla variante SXM5, che ne ha 128 flusso multiprocessore Per un totale di 16896 kernel CUDA fp32. Questa scheda ottiene 50 MB di cache L2 e 80 GB di memoria HBM3 sul bus di memoria a 5120 bit, per una larghezza di banda di memoria massima di circa 3 TB/s. Questa scheda ottiene 50 MB di cache L2 e 700 W tdp. Gli utenti possono combinare più GPU H100 SXM con l’interconnessione NVLink di Nvidia. Secondo Nvidia, il 4G offre larghezze di banda fino a 900 Gb/s.

Ci sarà anche una variante PCIe 5.0 x16 per server più standard. Questo modello riceve 114 messaggi di testo e 14.592 core CUDA. Inoltre, la variante PCIe ottiene una cache L2 da 40 MB, proprio come l’attuale A100. Sorprendentemente, la variante PCIe ha ancora una memoria HBM2e più lenta, secondo Pubblicato dal white paper di Nvidia Hopper martedì† A 80 GB, l’importo è uguale al modello SXM. La variante PCIe ottiene un tdp di 350 W.

Nuove caratteristiche della tramoggia: azionamento adattatore, set di istruzioni DPX

Anche l’architettura di Hopper è stata adattata rispetto ad Ampere. Hopper e H100 sono dotati di un nuovo motore switch, che combina un nuovo tipo di core Tensor con una suite software per l’elaborazione dei formati fp8 e fp16 per l’addestramento della rete di switch. Questo è un tipo di modello di apprendimento profondo.

Per il cloud computing, l’H100 può essere suddiviso in un massimo di sette casi† Ampere era già in grado di farlo, ma con Hopper erano completamente isolati l’uno dall’altro. Inoltre, Hopper ottiene un nuovo set di istruzioni DPX dedicato alla programmazione dinamica. Nvidia afferma che l’H100 ha prestazioni fino a sette volte migliori rispetto all’A100 senza DPX in questo caso d’uso.

Sistemi DGX e SuperPod

Nvidia offre anche il sistema DGX H100 con otto GPU H100. Con le sue otto GPU H100, questo sistema dispone di 640 GB di memoria HBM3 con una larghezza di banda totale di 24 TB/s. Gli utenti possono integrare fino a 32 sistemi DGX tramite connessioni NVLink. Nvidia lo chiama DGX SuperPod. Un tale sistema a 32 nodi dovrebbe offrire un’enorme potenza di calcolo, afferma Nvidia. Questo indica la potenza di calcolo fp8. L’azienda sta costruendo un supercomputer EOS, composto da 18 SuperPod DGX con un totale di 4.608 GPU H100.

Nvidia deve ancora annunciare il costo della GPU H100. Inoltre non è ancora chiaro quale sarà il costo dei sistemi H100 DGX o dei DGX H100 SuperPods. Inoltre, Hopper non dovrebbe essere utilizzato nelle GPU consumer. Entro la fine dell’anno, è stato riferito che Nvidia introdurrà la propria architettura Lovelace per le nuove schede grafiche GeForce RTX.

| Nvidia Hopper insieme alle precedenti GPU Nvidia HPC | |||

|---|---|---|---|

| costruzione | Huber | Ampere | Volta |

| GPU | H100, TSMC 4 nm | GA100, TSMC 7 nm | GV100, TSMC 12 nm |

| morire in superficie | 814 mm² | 826 mm² | 815 mm² |

| transistor | 80 miliardi | 54 miliardi | 21,1 miliardi |

| Core CUDA (fp32) | SXM: 16896 Slot PCIe: 14.592 |

6912 | 5120 |

| nuclei tensoriali | SXM: 528 PCIe: 456 |

432 | 640 |

| memoria | SXM: 80 GB HBM3 PCIe: 80 GB HBM2e |

40 GB / 80 GB HBM2e | 16 GB / 32 GB HBM2.0 |

| trasportatore FP32 | SXM: 60 flop PCIe: 48 Tflops |

19,5 flop | 15,7 flop |

| FP 64. Vettore | SXM: 30 flop PCIe: 24 Tflops |

9,7 flop | 7,8 flop |

| FP16 Tenditore | SXM: 1000 Tflops PCIe: 800 Tflops |

312 flop | 125 colpi |

| Tensore TF32 | SXM: 500 colpi PCIe: 400 Tflops |

156 flop | Non disponibile |

| FP64 Tenditore | SXM: 60 flop PCIe: 48 Tflops |

19,5 flop | Non disponibile |

| INT8. motore | SXM: 2000 picchi PCIe: 1600 pezzi |

624 picchi | Non disponibile |

| Tdp | fino a 700 watt | fino a 400 watt | fino a 300 watt |

| Fattore di forma | SXM5 / PCIe 5.0 | SXM4 / PCIe 4.0 | SXM2/PCie 3.0 |

“TV fanatic. Internet addict. Travel evangelist. Aspiring entrepreneur. Amateur explorer. Writer.”

:quality(80)/cdn-kiosk-api.telegraaf.nl/cb9357f4-a9d5-11ec-bd5d-02c309bc01c1.jpg)